10月24日,由IEEE电路与系统协会(CASS)主办的国际集成电路与系统研讨会(ISICAS)秋季学校(北京)在北航集成电路学院成功举行。本届ISICAS由Yongfu Li教授(上海交通大学)、赵巍胜教授(北京欧美大片ppt免费大全)、Mohd Sawan教授(西湖大学)共同担任大会主席,由李赛副教授(北京欧美大片ppt免费大全)和张和副教授(北京欧美大片ppt免费大全)共同担任北京秋季学校分会主席。

在本次秋季学校的开幕环节,北航集成电路学院副院长胡远奇教授代表组委会致欢迎辞。胡老师首先向与会师生表示热烈欢迎,并指出本次秋季学校以"下一代AI芯片"为主题,特邀四位知名专家分享前沿研究成果,旨在为参会者提供全面的学术视角。

报告一:自旋存储与计算

东南大学蔡浩教授系统剖析了实现高可靠性、高密度MRAM(磁随机存取存储器)所面临的技术挑战,并展示了从器件层面到系统层面的协同设计方法。蔡老师详细讲解了如何通过设计技术协同优化框架平衡性能、密度与良率,以及稳定可靠的电源与访问电路设计方案。在计算范式方面,蔡老师进一步对比了数字、模拟及混合模式存内计算在精度、能效与面积上的权衡,并介绍了基于压控MRAM的伊辛机如何为组合优化问题提供高效的硬件求解途径,为新一代计算架构提供创新思路。

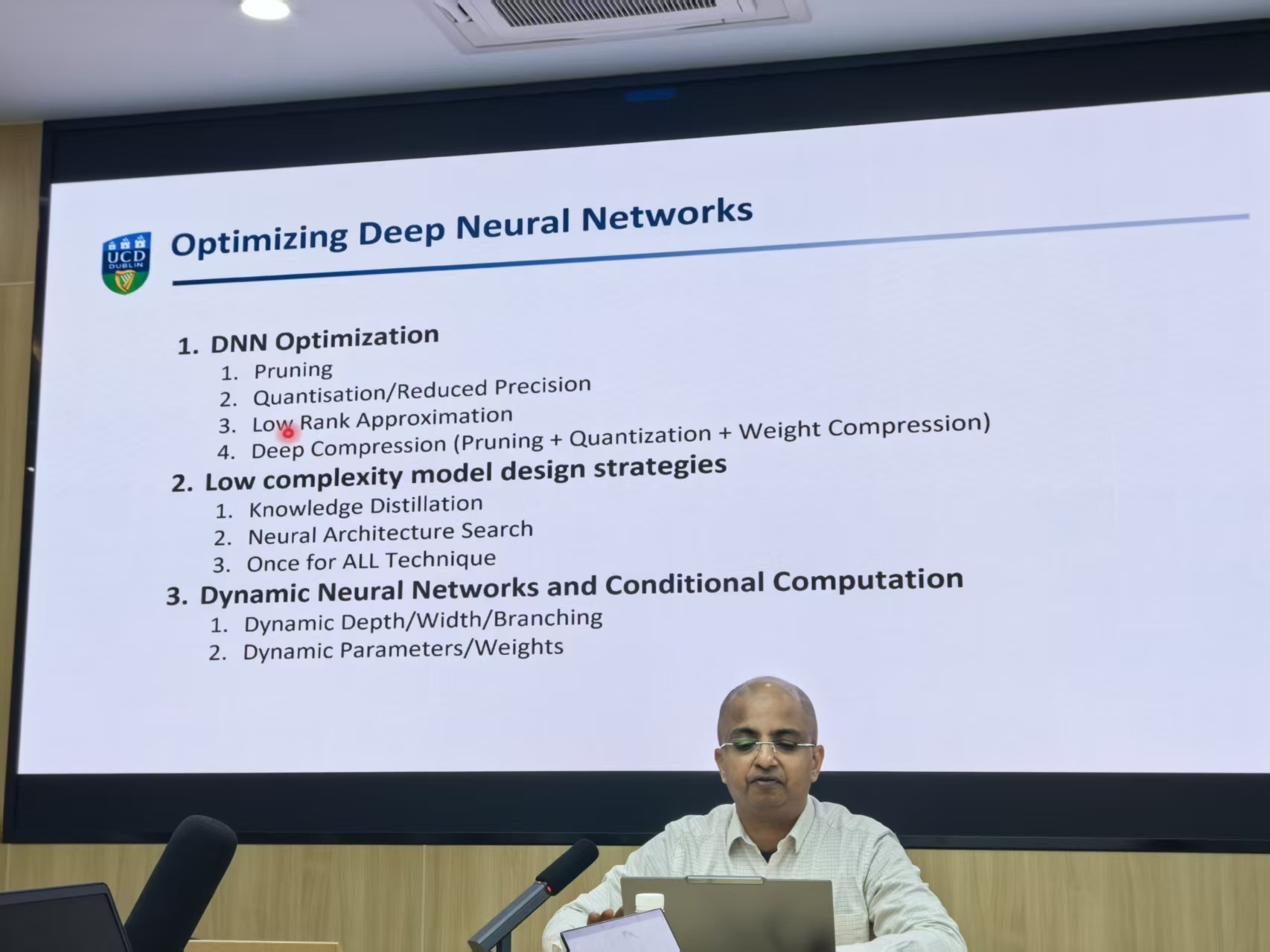

报告二:面向硬件设计的模型压缩与动态神经网络指南

爱尔兰都柏林大学Deepu John助理教授从硬件友好型AI模型的设计角度,系统阐述了包括结构化剪枝、低比特量化、低秩近似及知识蒸馏在内的多种轻量化技术。他特别分析了不同压缩技术在硬件部署中的实际代价与收益,并介绍了动态深度、宽度及参数化网络如何实现“按需计算”,有效提升推理能效。这些方法为构建算法-硬件协同优化的智能计算系统提供了扎实的理论依据与实用工具。

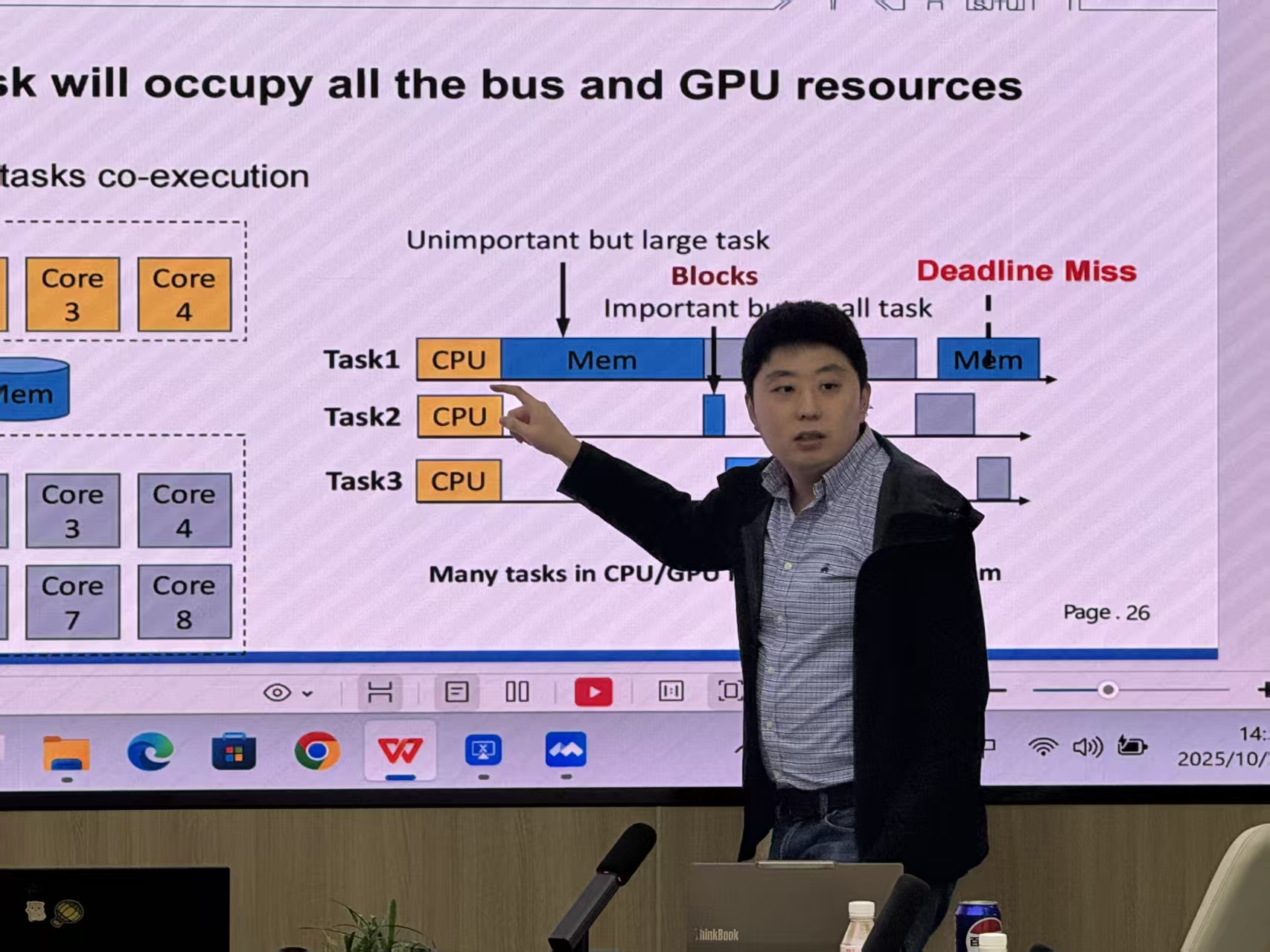

报告三:GPU与异构加速器上的实时计算

上海交通大学邹桉副教授从实时计算的任务需求出发,深入解析了GPU与专用加速器在并行架构、内存层次与计算单元设计上的特点与局限。他重点探讨了在动态与不确定负载下,如何通过硬件感知的静态与动态任务调度策略,保障关键任务的时序确定性。报告为在复杂异构平台上实现高效率、高确定性的并行处理提供了从架构到调度算法的系统级见解。

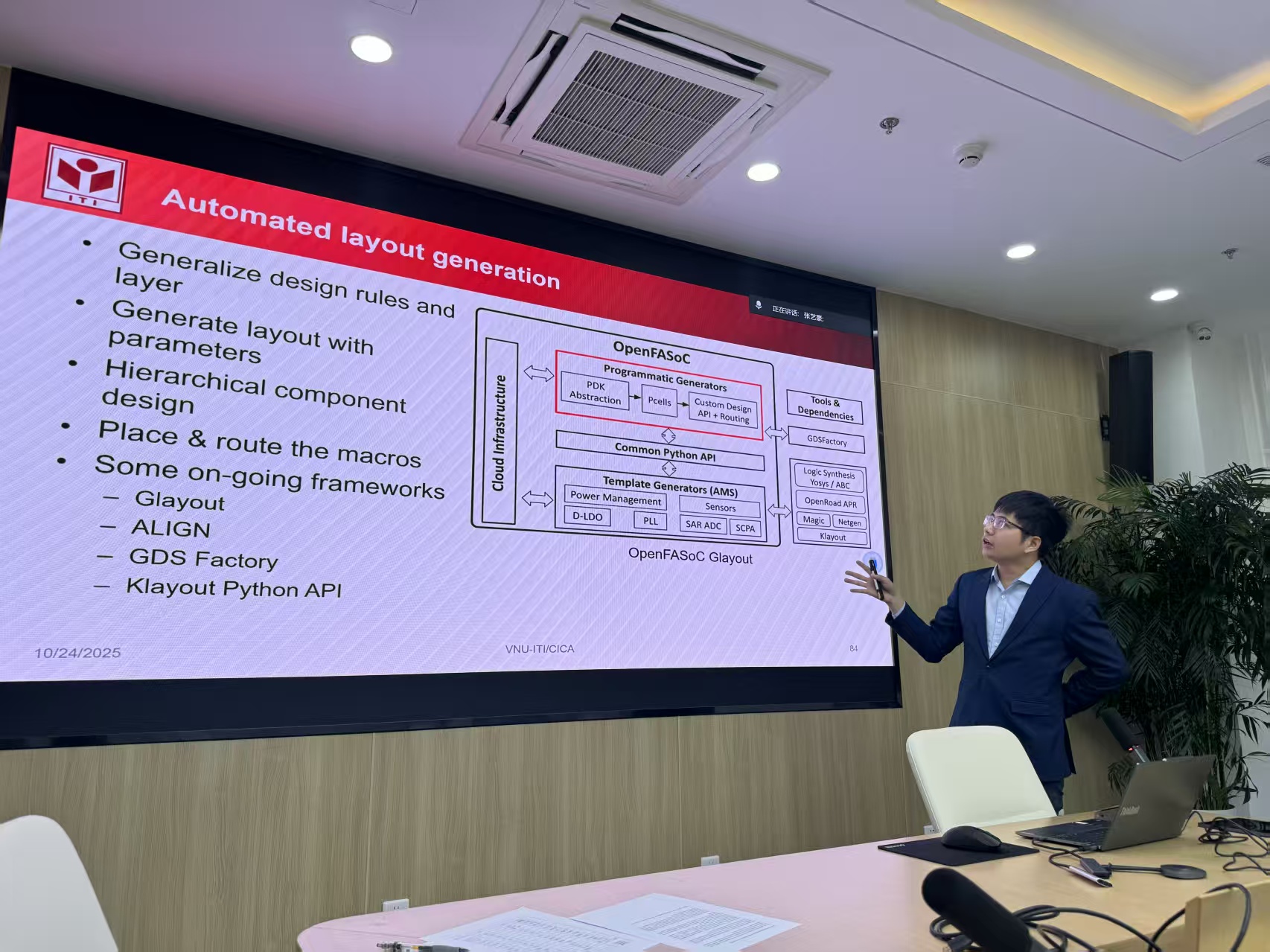

报告四:基于IHP SG13G2 PDK与开源工具的VLSI设计

越南国立大学Duy-Hieu Bui助理教授完整演示了基于开源EDA工具与IHP SG13G2工艺设计套件的芯片设计全流程。内容覆盖传统模拟/混合信号设计方法,以及使用OpenROAD实现从RTL到GDSII的自动数字设计流程。他特别引入了“Code-a-Chip”这一创新概念,通过可交互、可重复执行的设计笔记本来封装设计流程,显著提升了芯片设计的透明度与复现性,为快速、开放的芯片创新奠定了方法学基础。

活动现场交流氛围浓厚,学员们围绕报告内容积极提问,涉及技术原理、实现路径与发展前景等多个层面。专家对提问给予了专业而详尽的解答,深入的交流使学员们受益匪浅:既澄清了研究中的具体疑惑,又拓宽了学术视野,对前沿技术形成了更系统的认识。通过与专家的直接对话,学员们不仅深化了对专业知识的理解,更激发了科研热情,为后续的学术研究提供了新思路和新方向。

本次IEEE CASS主办的"下一代AI芯片"北京秋季学校成功搭建了高水平学术交流平台。活动系统梳理了从新型存算技术、算法-硬件协同到异构计算等关键技术路径,不仅拓宽了与会者的学术视野,更激发了创新思维,为领域内的人才培养和技术突破注入了新的活力。